搜索结果: 1-12 共查到“电子技术 VLSI”相关记录12条 . 查询时间(0.063 秒)

东南大学单伟伟、杨军团队在2019 Symposia VLSI Technology and Circuits国际会议发表高能效AES电路成果(图)

东南大学 单伟伟 杨军 2019 高能效 AES电路

2019/8/8

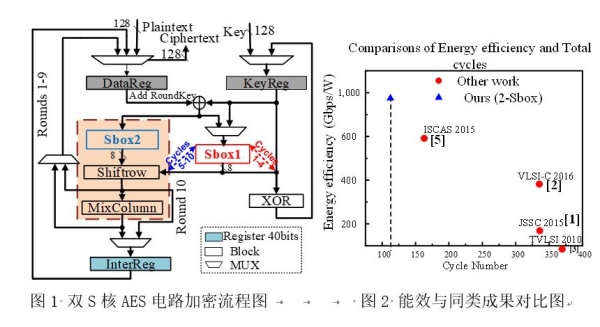

2019年6月9至14日,电子科学与工程学院单伟伟教授、杨军教授等赴日本参加Symposia VLSI Technology and Circuits会议。单伟伟教授在Symposium on VLSI Circuits分会的C20 session作报告,主题为“A 923Gbps/W, 113-Cycle, 2-Sbox Energy-efficient AES Accelerator in 2...

中国科学院微电子研究所在2019 VLSI国际研讨会上展示最新研究进展(图)

2019 VLSI 国际研讨会 研究进展

2019/6/25

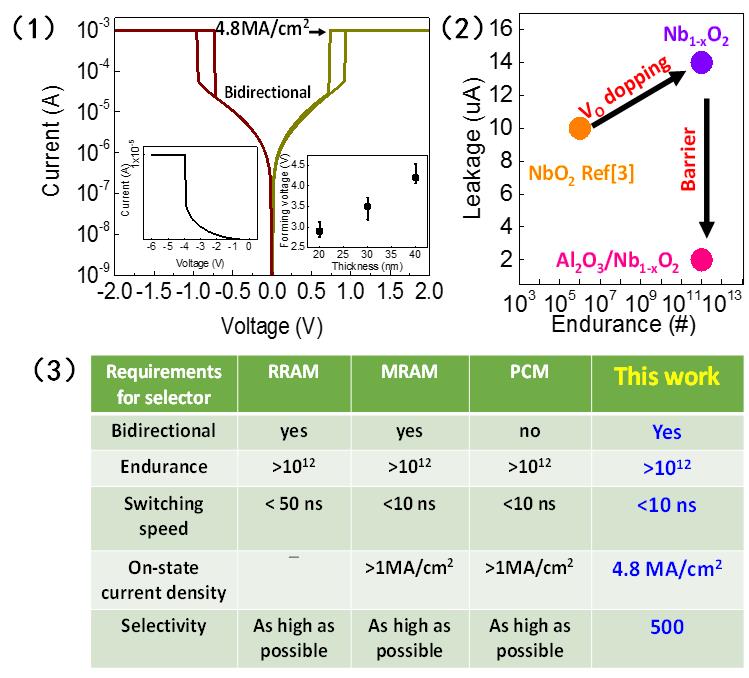

近日,2019 Symposia on VLSI Technology and Circuits(简称VLSI国际研讨会)在日本召开。微电子所刘明院士科研团队在会上展示了高性能选通管的最新研究进展。

Configuration of VLSI Arrays in the Presence of Defects

Circuit area fault tolerance percolation theory probabilistic analysis queuing processes systolic arrays

2015/8/14

The penalties for configuring VLSI arrays for yield enhancement are assessed. Each dement of the fabricated array is assumed to be defective with independent probability p. A fixed fractmn R of the el...

基于标准单元的低功耗FIR数字滤波器VLSI实现

低功耗 FIR滤波器 集成电路

2009/4/17

功耗与硅面积一样已成为芯片设计中的关键问题,尤其是在数字信号处理集成电路设计中。基于标准单元的VLSI设计是实现数字信号处理模块芯片或模块的重要方法。该文提出了一种基于标准单元的低功耗FIR滤波器多层次设计方案,其中体系结构层次采用多层流水线策略,逻辑层次将加法集成到部分积压缩中,在电路层次采用最小器件,从而在最大限度减少面积的同时降低了FIR的功耗。根据实际需求,该设计方案易于扩展和变换,可灵活...

本文介绍一种双线异或电路的构成单元,它能方便地向横向与纵向扩展,从而有利于VLSI电路的设计.文中给出了采用该单元构成的具有自校验特性的3个电路的设计,它们是XOR阵列,比较器和择多表决器.

1微米级VLSI专用电路工艺技术研究

VLSI 电路工艺

2008/11/25

该成果主要内容包括:完成了1.5μm成套工艺开发及1Mb汉字ROM研制,并实现了向工业化转移;完成了工艺线以3英寸到4英寸的升级改造,达到了攻关合同规定的量产能力并形成了多品种加工能力;开发了9种工艺模块技术,其中E2 PROM工艺和低漏电器件工艺属国内领先;开发了9种工艺监测与诊断用的PCM;开发了一套VISI-CAM系统,具有操作方便、信息量大、容错性强等特点。该成果为我国自行开发VISI成套...

成果内容简介、关键技术、技术经济指标:清华大学微电子学研究所通过“八五”攻关,已经建设成为中国1微米级VLSI设计和工艺加工的重要研究开发基地,经济效益分析;在完成“八五”攻关任务过程中,清华大学微电子学研究所十分重视科技为经济建设服务,把开发适宜国内产业的实用技术和有市场需求的产品,作为攻关的重点,因而取得了显著的经济和社会效益。

数字信号处理VLSI实现的可测性设计研究

可测性 数字信号处理 VLSI

2008/9/4

该课题针对当前数字信号处理对高速、高性能、高可靠性和低功耗的客观需求,以VISL实现数字信号处理的低功耗、可测试性设计为研究对象,研究数字信号变换与运算在阵列化、并行化和流水化VISL实现的可测性设计理论与方法,以及并行流水化数字滤波器VISL实现中的可测性设计问题。

RS码译码器的VLSI设计

RS码译码器 极高速集成电路硬件描述语言 现场可编程逻辑阵列

2008/6/30

本文主要研究RS码译码器的VLSI,设计优化方法。分析RS码译码算法的原理,将适合计算机仿真计算的算法转换成适合硬件实现的结构,并对其进行优化。设计并实现在FPGA上可以工作在10MHz时钟频率下的单周期硬件译码器。

An Efficient VLSI Implementation of MC Interpolation for MPEG-4

Efficient VLSI Implementation MC Interpolation MPEG-4

2010/12/14

Quarter sample mode interpolation is one of critical paths of the MPEG-4 decoder Because it has a finite

impulse response(FIR) digital filter which is a computationally expensive process. Normal FIR ...

A New Statistical Method for Maximum Power Estimation in CMOS VLSI Circuits

Maximum power reliability CMOS VLSI circuits statistics extremes

2010/12/8

A method for maximum power estimation in CMOS VLSI circuits is proposed. The method is based on extreme value theory and allows for the calculation of the upper end point of the probability distributi...