搜索结果: 1-10 共查到“Finfet”相关记录10条 . 查询时间(0.032 秒)

中国科学院微电子研究所专利:一种FinFet器件源漏外延设备

中国科学院微电子研究所 专利 FinFet器件 源漏外延

2023/7/11

近日,中国科学院微电子研究所集成电路先导工艺研发中心,面向5纳米及以下节点高性能和低功耗晶体管性能需求,基于主流后高K金属栅(HKMG-last)三维FinFET器件集成技术,成功研制出高性能的负电容FinFET器件。现有硅基晶体管受玻尔兹曼热力学限制,室温下亚阈值摆幅SS≥60mV/dec,阻碍了工作电压的继续降低。当集成电路技术进入5纳米及以下节点,随着集成度的持续增加,在维持器件性能的同时面...

近日,微电子所集成电路先导工艺研发中心,面向5纳米及以下节点高性能和低功耗晶体管性能需求,基于主流后高K金属栅(HKMG-last)三维FinFET器件集成技术,成功研制出高性能的负电容FinFET器件。现有硅基晶体管受玻尔兹曼热力学限制,室温下亚阈值摆幅SS≥60mV/dec,阻碍了工作电压的继续降低。当集成电路技术进入5纳米及以下节点,随着集成度的持续增加,在维持器件性能的同时面临功耗急剧增加...

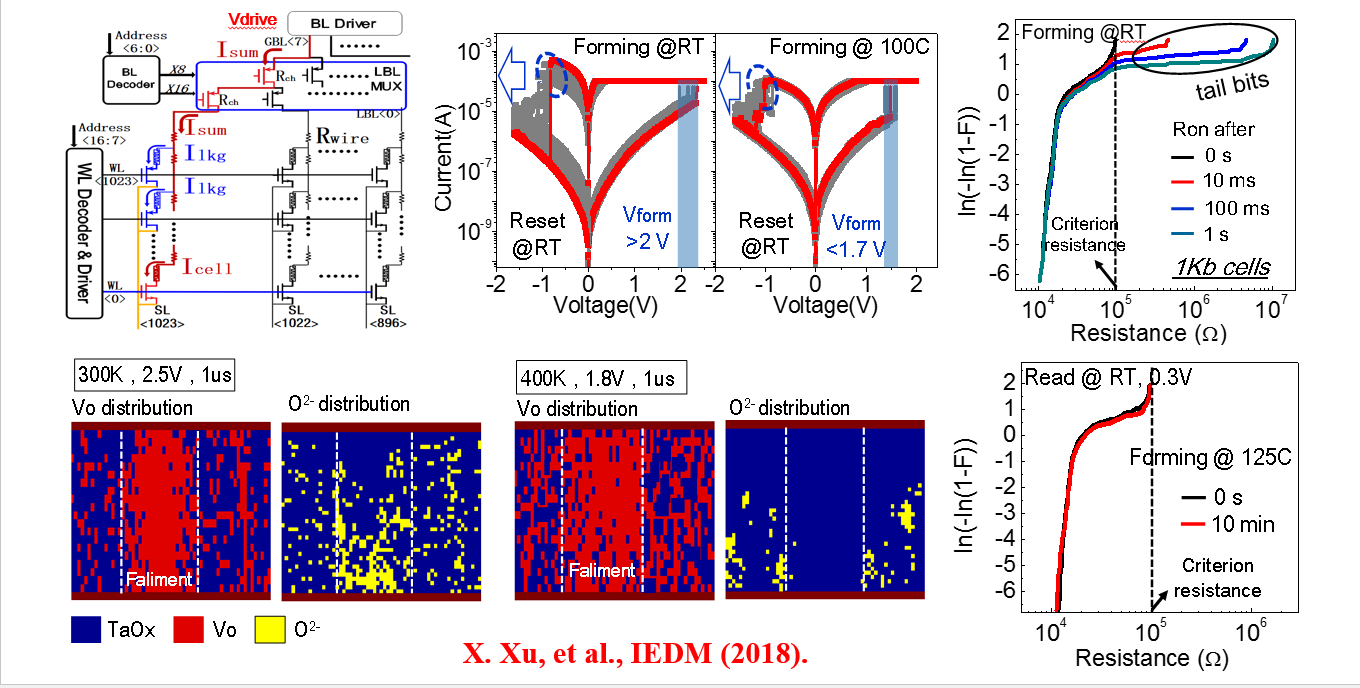

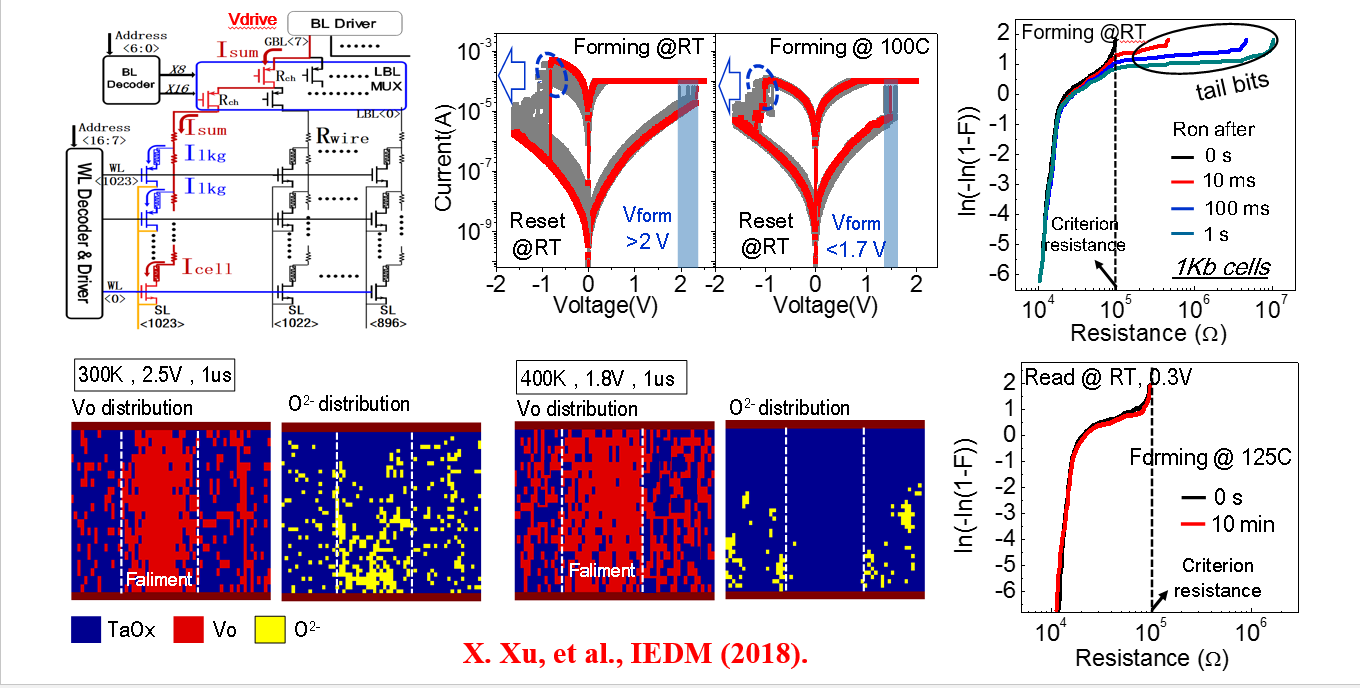

近日,2018国际电子器件大会(IEDM)在美国旧金山召开。会上,中国科学院院士、中国科学院微电子研究所研究员刘明团队展示了28纳米嵌入式阻变存储器可靠性优化以及基于HfZrO铁电FinFET器件的最新研究成果。对于新型存储器RRAM,初始电形成过程会增加电路设计复杂度,带来可靠性问题,一直是工业界和科研界研究的热点。刘明团队在RRAM方向的研究具有丰富的经验,针对28纳米的1Mb RRAM测试芯...

近日,2018国际电子器件大会(IEDM)在美国旧金山召开。会上,微电子所刘明院士科研团队展示了28纳米嵌入式阻变存储器可靠性优化以及基于HfZrO铁电FinFET器件的最新研究成果。对于新型存储器RRAM,初始电形成过程会增加电路设计复杂度,带来可靠性问题,一直是工业界和科研界研究的热点。刘明院士团队在RRAM方向的研究具有丰富的经验,针对28纳米的1Mb RRAM测试芯片(IEDM 2017 ...

近日,中国科学院微电子研究所集成电路先导工艺研发中心(十室)在集成电路面向7纳米及以下技术代的“Post-FinFET”器件研究中取得新进展。

FinFET器件是当前16/14纳米节点集成电路工艺技术的关键架构。由于沟道静电势控制问题,7纳米及以下技术代的研发面临严重的技术挑战。环栅纳米线器件因具有优异的静电完整性和弹道输运特性,被公认为最有希望取代FinFET并应用在7纳米以下节点的理想器件结...